# **DECT Single-Chip Transceiver**

#### Description

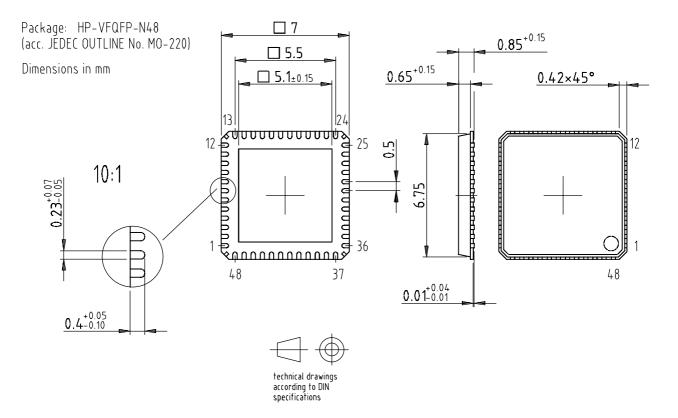

The T2801 is an RF IC for low-power DECT applications. The HP-VFQFP-N48–packaged IC is a complete transceiver including image rejection mixer, IF amplifier, FM demodulator, baseband filter, RSSI, TX preamplifier, power-ramping generator for power amplifiers, integrated synthesizer, fully integrated VCO, TX filter and modulation compensation circuit for advanced closedloop modulation concept. No mechanical tuning is necessary in production.

#### Features

- Supply-voltage range 3 V to 4.6 V (unregulated)

- Auxiliary-voltage regulator on-chip

- Low current consumption

- Few low cost external components

- No mechanical tuning required

## • Non-blindslot and blindslot operation

- Unlimited multislot operation with advanced closedloop modulation (13.824 MHz/ 27.648 MHz and 10.368 MHz/ 20.736 MHz)

- TX preamplifier with 0 dBm output power at 1.9 GHz and ramp-signal generator for SiGe power amplifier

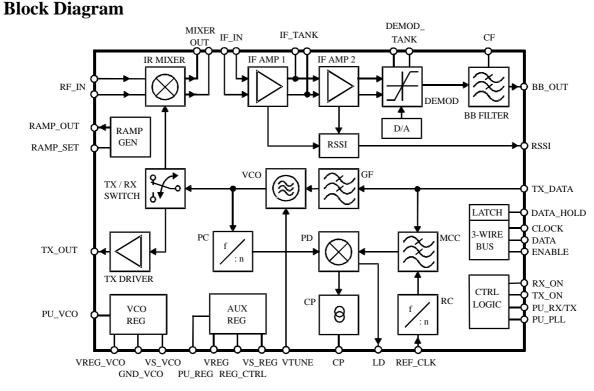

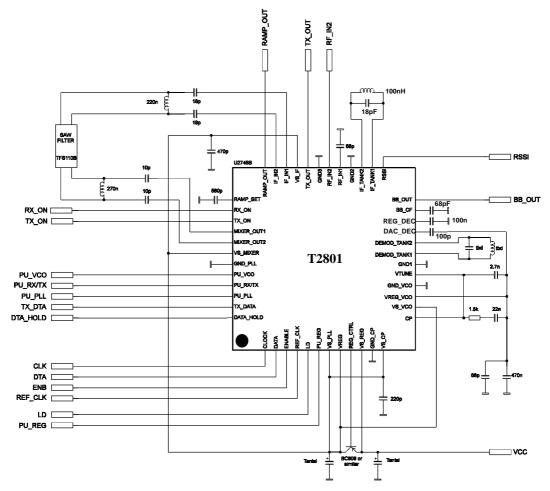

Figure 1. Block diagram

#### **Ordering Information**

| Extended Type Number | Package      | Remarks          |

|----------------------|--------------|------------------|

| T2801-PLT            | HP-VFQFP-N48 | Tray             |

| T2801-PLQ            | HP-VFQFP-N48 | Taped and reeled |

## **Pin Description**

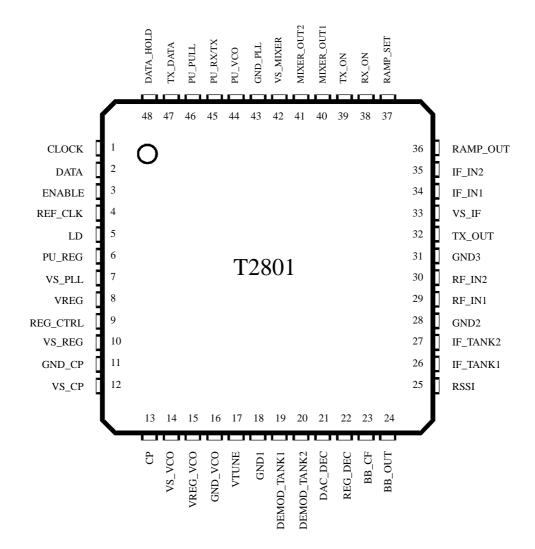

| Figure  | 2. | Pin    | ning |

|---------|----|--------|------|

| 1 iguic | 2. | 1 1111 | ms   |

| Pin | Symbol | Function                 | Configuration |

|-----|--------|--------------------------|---------------|

| 1   | CLOCK  | 3-wire-bus: Clock input  |               |

| 2   | DATA   | 3-wire-bus: Data input   |               |

| 3   | ENABLE | 3-wire-bus: Enable input |               |

# **Preliminary Information**

| Pin | Symbol  | Function                              | Configuration                                                                                                                                                                                                                                                                                                                                       |

|-----|---------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | REF_CLK | Reference-frequency input             |                                                                                                                                                                                                                                                                                                                                                     |

| 5   | LD      | Lock-detect output                    |                                                                                                                                                                                                                                                                                                                                                     |

| 6   | PU_REG  | Aux. voltage regulator power-up input | PU_REG<br>6 0 25k 25k                                                                                                                                                                                                                                                                                                                               |

| 7   | VS_PLL  | PLL supply voltage                    | VS_REG VS_PLL<br>10 $\lor$ VS_CP<br>12 $\lor$ VS_VCO<br>14 $\lor$ VS_VCO<br>14 $\lor$ VS_JF<br>VS_MIXER<br>42 $\lor$ GND1<br>11 $\lor$ GND2<br>16 $\lor$ GND3<br>31 $\circ$ VS_MIXER<br>GND3 $\lor$ GND2<br>GND_PLL<br>31 $\circ$ VS_MIXER<br>GND_VCO<br>16 $\lor$ VS_MIXER<br>GND3 $\lor$ CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO<br>CO |

| Pin | Symbol   | Function                                | Configuration |

|-----|----------|-----------------------------------------|---------------|

| 8   | VREG     | Aux. voltage-regulator output           |               |

| 9   | REG_CTRL | Aux. voltage-regulator control output   |               |

| 10  | VS_REG   | Aux. voltage-regulator supply voltage   |               |

| 11  | GND_CP   | Charge-pump ground                      |               |

| 12  | VS_CP    | Charge-pump supply voltage              |               |

| 13  | СР       | Charge-pump output                      | GND_CP        |

| 14  | VS_VCO   | VCO voltage-regulator supply voltage    | vs_vco<br>14  |

| 15  | VREG_VCO | VCO voltage-regulator control<br>output | vreg_vco<br>+ |

| 16  | GND_VCO  | VCO ground                              |               |

| 17  | VTUNE    | VCO tuning voltage input                |               |

**T2801**

| Pin | Symbol      | Function                   | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | GND1        | Ground                     | VS_REG VS_PLL<br>10 VS_CP<br>12 VS_VCO<br>14 VS_VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |             |                            | GND_CP<br>110<br>GND_VCO<br>160<br>GND3<br>GND3<br>GND3<br>GND3<br>GND3<br>GND4<br>GND4<br>GND4<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND2<br>GND4<br>GND2<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4<br>GND4 |

| 19  | DEMOD_TANK1 | Demodulator tank circuit   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20  | DEMOD_TANK2 | Demodulator tank circuit   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21  | DAC_DEC     | Decoupling PIN for VCO_DAC | $\begin{array}{c} & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22  | REG_DEC     | Decoupling PIN for REG     | REG_DEC<br>C<br>21<br>Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin | Symbol   | Function                                          | Configuration           |

|-----|----------|---------------------------------------------------|-------------------------|

| 23  | BB_CF    | Baseband filter corner-frequency<br>control input |                         |

| 24  | BB_OUT   | Baseband filter output                            |                         |

| 25  | RSSI     | Received signal-strength indicator<br>output      | VS<br>RSSI<br>25<br>15k |

| 26  | IF_TANK1 | IF tank circuit                                   |                         |

| 27  | IF_TANK2 | IF tank circuit                                   |                         |

# Preliminary Information

| Pin | Symbol | Function                                       | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | GND2   | Ground                                         | VS_REG VS_PLL<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |        |                                                | $\begin{array}{c} 42 \circ \\ \hline GND_CP \\ 11 \circ \\ \hline \\ GND_VCO \\ 16 \circ \\ \hline \\ GND3 \\ 31 \circ \\ \hline \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 29  | RF_IN1 | Differential RF input of image<br>reject mixer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30  | RF_IN2 | Differential RF input of image reject mixer    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 31  | GND3   | Ground                                         | VS_REG VS_PLL<br>10 $\vee$ VS_CP<br>12 $\vee$ VS_VCO<br>14 $\vee$ VS_VCO<br>14 $\vee$ VS_IF<br>VS_MIXER<br>42 $\vee$ GND1<br>10 $\vee$ GND1<br>10 $\vee$ GND2<br>16 $\vee$ GND3<br>10 $\vee$ GND3<br>10 $\vee$ GND2<br>10 $\vee$ GND3<br>10 $\vee$ GND2<br>10 $\vee$ GND3<br>10 $\vee$ GND2<br>10 $\vee$ GND2<br>10 $\vee$ GND3<br>10 $\vee$ GND3 |

| Pin | Symbol | Function                              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32  | TX_OUT | TX driver amplifier output for PA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 33  | VS_IF  | IF amplifier supply voltage           | VS_REG VS_PLL<br>10 $\lor$ VS_PLL<br>10 $\lor$ VS_CP<br>12 $\lor$ VS_VCO<br>14 $\lor$ VS_VCO<br>14 $\lor$ VS_JF<br>33 $\lor$ VS_MIXER<br>42 $\lor$ GND1<br>10 $\lor$ VS_MIXER<br>42 $\lor$ GND2<br>16 $\lor$ VS_MIXER<br>GND3 $\lor$ GND2<br>16 $\lor$ VS_MIXER<br>GND3 $\lor$ VS_MIXER<br>GND PLL<br>31 $\circ$ VS_MIXER<br>GND PLL<br>31 $\circ$ VS_MIXER<br>GND PLL<br>31 $\circ$ VS_MIXER<br>GND PLL<br>31 $\circ$ VS_MIXER<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT<br>COMPARENT |

| 34  | IF_IN1 | Differential IF input of IF amplifier |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35  | IF_IN2 | Differential IF input of IF amplifier |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# Preliminary Information

| Pin | Symbol     | Function                                      | Configuration                                                                                     |

|-----|------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|

| 36  | RAMP_OUT   | Ramp-generator output for PA<br>power ramping | VS<br>B<br>B<br>B<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C |

| 37  | RAMP_SET   | Slew-rate setting of ramping signal           | VS<br>T<br>RAMP_SET                                                                               |

| 38  | RX_ON      | RX control input                              |                                                                                                   |

| 39  | TX_ON      | TX control input                              | 38, 39<br>5k<br>5k<br>5k<br>5k<br>5k<br>5k<br>5k<br>5k<br>5k<br>5k                                |

| 40  | MIXER_OUT1 | Differential mixer output for<br>SAW filter   |                                                                                                   |

| 41  | MIXER_OUT2 | Differential mixer output for<br>SAW filter   |                                                                                                   |

| Pin | Symbol   | Function             | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42  | VS_MIXER | Mixer supply voltage | VS_REG VS_PLL<br>10 VS_CP<br>12 VS_VCO<br>14 VS_IF<br>33 VS_VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 43  | GND_PLL  | PLL ground           | $\begin{array}{c} VS_MDXER \\ 42 \\ GND_CP \\ 11 \\ GND_VCO \\ 16 \\ GND_3 \\ 31 \\ H \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 44  | PU_VCO   | VCO power-up input   | PU_VCO<br>PU_RX/TX<br>44, 45 25k 25k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 45  | PU_RX/TX | RX/TX power-up input |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 46  | PU_PLL   | PLL power-up input   | 20k $10k$ $10k$ $10k$ $10k$ $25k$ |

| Pin | Symbol    | Function                                                                | Configuration                                                                                    |

|-----|-----------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 47  | TX_DATA   | TX data input of Gaussian filter and<br>modulation-compensation circuit | TX_DATA<br>47<br>5k<br>5k<br>5k<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| 48  | DATA_HOLD | Data-hold input to keep the latch<br>information in power-down mode     | DATA_HOLD<br>48 O<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T               |

#### **Functional Description**

#### Receiver

The RF-input signal at RF\_IN is fed to an image rejection mixer IR\_MIXER with its differential outputs MIXER\_OUT1 and MIXER\_OUT2 driving an IF-SAW filter at 110 MHz or 111 MHz. The IF amplifiers IF\_AMP1 and IF\_AMP2 with an external IF\_TANK and an integrated RSSI function feed the signal to the demodulator DEMOD working at  $f = f_{IF}/2$  (55 MHz/ 55.5 MHz) and finally to an integrated baseband filter BB. For demodulator tuning in production an integrated 5-bit digital-to-analog (D/A) converter is used to control the on-chip varicap diode.

#### Transmitter

The transmit data at TX\_DATA is filtered by an integrated Gaussian filter GF and fed to the fully integrated VCO operating at twice the output frequency. After modulation the signal is frequency-divided by 2 and fed via a TX/RX SWITCH to the TX\_DRIVER. This bus-controlled driver amplifier supplies +3 dBm output power at TX\_OUT. A ramp-signal generator RAMP\_GEN, providing ramp signals at RAMP\_OUT for an external power amplifier, is also integrated. The slope of the ramp signal is controlled by a capacitor at RAMP\_SET.

#### Synthesizer

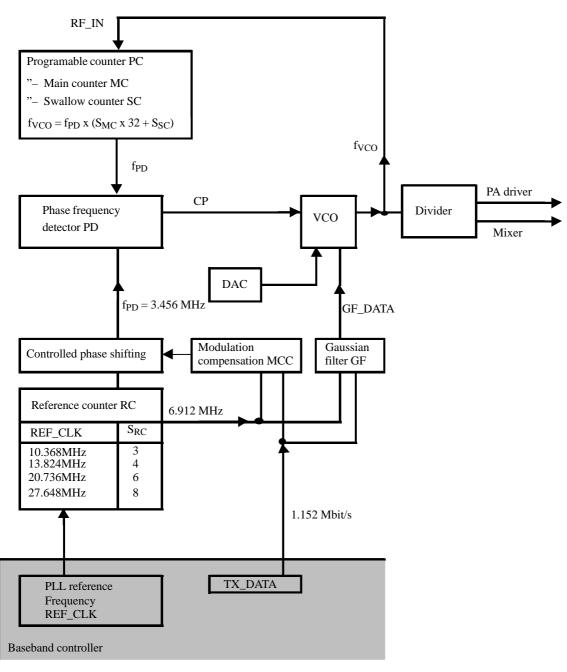

The IR\_MIXER, the TX\_DRIVER and the programmable counter PC are driven by the fully integrated VCO (including on-chip inductors and varactors). An 3-bit digital-to-analog converter is used to pretune the frequency. The output signal is frequency-divided to supply the desired frequency to the TX\_DRIVER, 0/90 degree phase shifter for the IR\_MIXER and to be used by the PC for the phase detector PD ( $f_{PD} = 3.456$  MHz). Unlimited multislot operation is possible by using the integrated advanced closed-loop modulation concept based on the modulation compensation circuit MCC.

#### **Power Supply**

For minimum interference and maximum signal isolation an integrated bandgap-stabilized voltage regulator for use with an external low-cost PNP transistor is implemented. Multiple power-down and current saving modes are provided.

## **PLL Principle**

Figure 3.

The following table shows the LO frequencies for RX and TX for the DECT band plus additional channels for an optional DECT band extension. Intermediate frequencies of 110.592 and 112.32 MHz are supported. Table 1. LO frequencies

| Mode | f <sub>IF</sub> /MHz | Channel | f <sub>ANT</sub> /MHz | f <sub>VCO</sub> /MHz | f <sub>VCO</sub> /2/MHz | S <sub>MC</sub> | S <sub>SC</sub> |

|------|----------------------|---------|-----------------------|-----------------------|-------------------------|-----------------|-----------------|

| TX   |                      | C9      | 1881.792              | 3763.584              | 1881.792                | 34              | 1               |

|      |                      | C8      | 1883.520              | 3767.040              | 1883.520                | 34              | 2               |

|      |                      |         |                       |                       |                         |                 |                 |

|      |                      | C1      | 1895.616              | 3791.232              | 1895.616                | 34              | 9               |

|      |                      | CO      | 1897.344              | 3794.688              | 1897.344                | 34              | 10              |

|      |                      | C10     | 1899.072              | 3798.144              | 1899.072                | 34              | 11              |